## SGM829 Low Quiescent Current, Programmable Delay Supervisory Circuit

## **GENERAL DESCRIPTION**

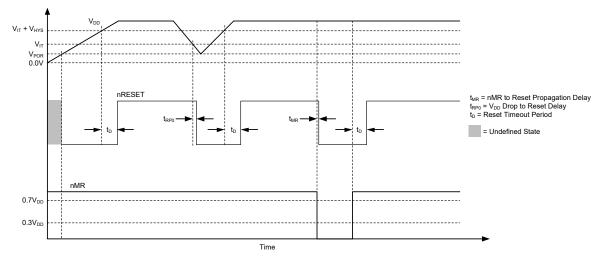

The SGM829 family can monitor system voltages from 1.8V to 5V. When the  $V_{DD}$  voltage drops below a preset threshold ( $V_{IT}$ ) or the manual reset (nMR) pin is driven low, the open-drain nRESET output is asserted. After the  $V_{DD}$  voltage and nMR voltage return above their respective thresholds, the nRESET output remains low within the user-adjustable delay time.

The SGM829 uses a precision reference to achieve 1% threshold accuracy. The reset timeout period can be set to 0.29ms by leaving the SRT pin open, or can be programmed from 1.25ms to 10s by connecting the SRT pin to an external capacitor. Low quiescent current makes SGM829 very suitable for battery-powered applications.

The SGM829 is available in a Green SOT-23-5 package.

## **FEATURES**

- Adjustable Reset Timeout Period: 1.25ms to 10s

- Low Quiescent Current: 0.6µA (TYP)

- High Threshold Accuracy: 1% (TYP)

- Factory-Set Detection Voltages from 1.8V to 5V

- Manual Reset (nMR) Input

- Open-Drain nRESET Output

- Available in a Green SOT-23-5 Package

## **APPLICATIONS**

Portable and Battery-Powered Products FPGA and ASIC Applications DSP or Microcontroller Applications Notebook and Desktop Computers

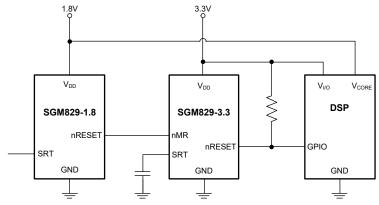

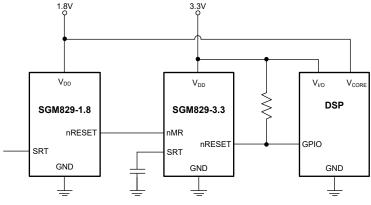

# TYPICAL APPLICATION

#### Figure 1. Typical Application Circuit

### **PACKAGE/ORDERING INFORMATION**

| MODEL      | THRESHOLD<br>VOLTAGE (VIT) (V) | PACKAGE<br>DESCRIPTION | ORDERING<br>NUMBER | PACKAGE<br>MARKING | PACKING<br>OPTION   |

|------------|--------------------------------|------------------------|--------------------|--------------------|---------------------|

| SGM829-1.8 | 1.67                           | SOT-23-5               | SGM829-1.8XN5G/TR  | R70XX              | Tape and Reel, 3000 |

| SGM829-1.9 | 1.77                           | SOT-23-5               | SGM829-1.9XN5G/TR  | R72XX              | Tape and Reel, 3000 |

| SGM829-2.5 | 2.33                           | SOT-23-5               | SGM829-2.5XN5G/TR  | R75XX              | Tape and Reel, 3000 |

| SGM829-2.7 | 2.52                           | SOT-23-5               | SGM829-2.7XN5G/TR  | R77XX              | Tape and Reel, 3000 |

| SGM829-2.9 | 2.7                            | SOT-23-5               | SGM829-2.9XN5G/TR  | R79XX              | Tape and Reel, 3000 |

| SGM829-3.0 | 2.79                           | SOT-23-5               | SGM829-3.0XN5G/TR  | R3CXX              | Tape and Reel, 3000 |

| SGM829-3.3 | 3.07                           | SOT-23-5               | SGM829-3.3XN5G/TR  | R7BXX              | Tape and Reel, 3000 |

| SGM829-3.7 | 3.45                           | SOT-23-5               | SGM829-3.7XN5G/TR  | R7DXX              | Tape and Reel, 3000 |

| SGM829-4.0 | 3.73                           | SOT-23-5               | SGM829-4.0XN5G/TR  | R7FXX              | Tape and Reel, 3000 |

| SGM829-4.5 | 4.2                            | SOT-23-5               | SGM829-4.5XN5G/TR  | R81XX              | Tape and Reel, 3000 |

| SGM829-5.0 | 4.65                           | SOT-23-5               | SGM829-5.0XN5G/TR  | R83XX              | Tape and Reel, 3000 |

### **MARKING INFORMATION**

NOTE: XX = Date Code.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to GND            | -0.3V to 7V                    |

|-----------------------------------|--------------------------------|

| SRT to GND                        | 0.3V to V <sub>DD</sub> + 0.3V |

| nRESET, nMR to GND                | -0.3V to 7V                    |

| nRESET Pin Current                | ±5mA                           |

| Package Thermal Resistance        |                                |

| SOT-23-5, θ <sub>JA</sub>         | 245°C/W                        |

| Junction Temperature              | +150°C                         |

| Storage Temperature Range         | 65°C to +150°C                 |

| Lead Temperature (Soldering, 10s) | +260°C                         |

| ESD Susceptibility                |                                |

| HBM                               | 4000V                          |

| CDM                               |                                |

|                                   |                                |

### **RECOMMENDED OPERATING CONDITIONS**

| Input Supply Voltage Range, V <sub>DD</sub> | 1.65V to 6.5V         |

|---------------------------------------------|-----------------------|

| SRT Pin Voltage, V <sub>SRT</sub>           | V <sub>DD</sub> (MAX) |

| nMR Pin Voltage, V <sub>nMR</sub>           | 0V to 6.5V            |

| nRESET Pin Voltage, V <sub>nRESET</sub>     | 0V to 6.5V            |

| nRESET Pin Current, InRESET                 | 0.0003mA to 5mA       |

| Operating Junction Temperature Range        | 40°C to +125°C        |

### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

### DISCLAIMER

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

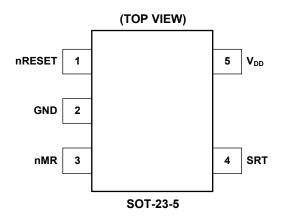

## **PIN CONFIGURATION**

## **PIN DESCRIPTION**

| PIN | NAME            | I/O | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----|-----------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | nRESET          | 0   | Active-Low Reset Output. When the V <sub>DD</sub> input is lower than V <sub>IT</sub> or the nMR pin is set to logic low, nRESET is asserted and driven to a low-impedance state. nRESET remains low (asserted) for the reset timeout period after both V <sub>DD</sub> exceeds V <sub>IT</sub> and nMR pin is driven high. A pull-up resistor from $10k\Omega$ to $1M\Omega$ should be used on this pin and allows the reset pin to attain voltages higher than V <sub>DD</sub> . |

| 2   | GND             | _   | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3   | nMR             | I   | Manual Reset Input Pin. Pulling this pin (nMR) low will assert nRESET. nMR is internally pulled up to $V_{DD}$ by a 100k $\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                        |

| 4   | SRT             | I   | Set Reset Timeout Input. Connect a capacitor between SRT and ground to set the timeout period.<br>The pin can be left open, but it cannot be connected to V <sub>DD</sub> . Determine the period as follows:<br>$T_D (\mu s) = (2.8 \times 10^6) \times C_{SRT} (\mu F) + 290 \mu s.$                                                                                                                                                                                              |

| 5   | V <sub>DD</sub> | I   | Supply Voltage. It is recommended to place a $0.1 \mu F$ ceramic capacitor close to this pin.                                                                                                                                                                                                                                                                                                                                                                                      |

NOTE: I: input, O: output.

## **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = 1.65V \text{ to } 6.5V, R_{LRESET} = 100 \text{k}\Omega^{(1)}, T_{J} = -40^{\circ}\text{C}$  to +85°C, typical values are at  $T_{J} = +25^{\circ}\text{C}$ , unless otherwise noted.)

| PARAMETER                                                     | SYMBOL               | CONDITIONS                                                              | MIN  | TYP                | MAX                 | UNITS |  |

|---------------------------------------------------------------|----------------------|-------------------------------------------------------------------------|------|--------------------|---------------------|-------|--|

| Input Supply Voltage Range                                    | V <sub>DD</sub>      |                                                                         | 1.65 |                    | 6.5                 | V     |  |

| Supply Current (Current inte )/ Din)                          |                      | V <sub>DD</sub> = 3.3V, nRESET not asserted,<br>nMR, nRESET, SRT open   |      | 0.6                | 1.5                 |       |  |

| Supply Current (Current into V <sub>DD</sub> Pin)             | I <sub>DD</sub>      | V <sub>DD</sub> = 6.5V, nRESET not asserted,<br>nMR, nRESET, SRT open   |      | 0.9                | 2                   | μA    |  |

|                                                               | V                    | $1.3V \le V_{DD} < 1.8V, I_{OL} = 0.4mA$                                |      |                    | 0.2                 | - v   |  |

| Low-Level Output Voltage                                      | V <sub>OL</sub>      | $1.8V \le V_{DD} \le 6.5V$ , $I_{OL} = 1mA$                             |      | 0.3                |                     | v     |  |

| Power-On Reset Voltage                                        | V <sub>POR</sub>     | $V_{OL_{MAX}} = 0.2V$ , $I_{nRESET} = 15\mu A$                          |      |                    | 0.8                 | V     |  |

|                                                               |                      | T <sub>J</sub> = +25°C                                                  | -1.0 |                    | 1.0                 | 0/    |  |

| Negative-Going Input Threshold Accuracy                       | V <sub>IT</sub>      | $T_J = -40^{\circ}C$ to $+85^{\circ}C$                                  | -1.3 |                    | 1.3                 | %     |  |

| Hysteresis on V <sub>IT</sub> <sup>(2)</sup> V <sub>HYS</sub> |                      |                                                                         |      | $50 \times V_{IT}$ |                     | mV    |  |

| V <sub>DD</sub> Drop to Reset Delay                           | t <sub>RP0</sub>     | Drop = $V_{IT}$ - 250mV,<br>T <sub>J</sub> = -40°C to +85°C             |      | 85                 |                     | μs    |  |

| nMR Internal Pull-Up Resistance                               | $R_{nMR}$            | $T_J = -40^{\circ}C$ to $+85^{\circ}C$                                  |      | 100                |                     | kΩ    |  |

|                                                               | VIH                  | H Logic high $0.7 \times V_{DD}$                                        |      |                    |                     |       |  |

| nMR Input                                                     | VIL                  | Logic low                                                               |      |                    | $0.3 \times V_{DD}$ | V     |  |

| Input Capacitance, Any Pin                                    | C <sub>IN</sub>      | SRT pin, $V_{IN}$ = 0V to $V_{DD}$ ,<br>T <sub>J</sub> = -40°C to +85°C |      | 5                  |                     | 'nE   |  |

| Input Capacitance, Any Fin                                    | CIN                  | Other pins, $V_{IN} = 0V$ to 6.5V,<br>T <sub>J</sub> = -40°C to +85°C   |      | 5                  |                     | pF    |  |

| nMR Glitch Rejection                                          |                      | $T_J = -40^{\circ}C$ to $+85^{\circ}C$                                  |      | 100                |                     | ns    |  |

| nMR to Reset Propagation Delay                                | t <sub>nMR</sub>     | $T_J = -40^{\circ}C$ to $+85^{\circ}C$                                  |      | 240                |                     | ns    |  |

|                                                               |                      | SRT open                                                                | 0.15 | 0.29               | 0.40                |       |  |

| Reset Timeout Period                                          | t <sub>D</sub>       | C <sub>SRT</sub> = 1nF                                                  | 1.5  | 2.8                | 4.0                 | ms    |  |

| SRT Source Current I <sub>RAMP</sub>                          |                      | $T_J = -40^{\circ}C$ to $+85^{\circ}C$                                  |      | 430                |                     | nA    |  |

| SRT Source Threshold Voltage                                  | V <sub>TH-RAMP</sub> | $T_J = -40^{\circ}C$ to $+85^{\circ}C$                                  |      | 1.205              |                     | V     |  |

#### NOTES:

- 1. RLRESET is the resistor connected to the nRESET pin.

- 2. Guaranteed by design and not tested in production.

SG Micro Corp

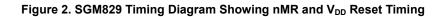

## **TYPICAL PERFORMANCE CHARACTERISTICS**

Test for SGM829-3.0 only,  $T_J$  = +25°C, unless otherwise noted.

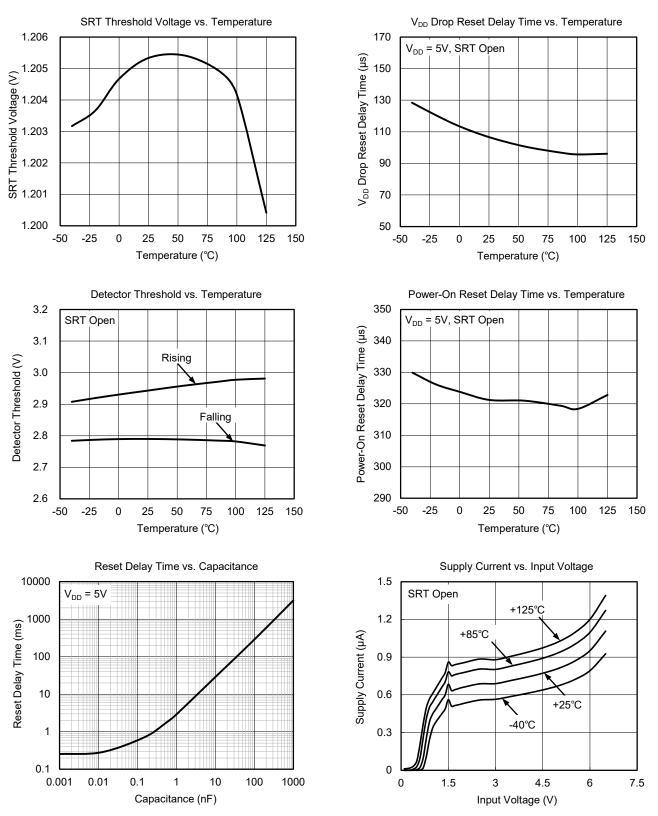

## FUNCTIONAL BLOCK DIAGRAM

### SGM829

### **DETAILED DESCRIPTION**

When the  $V_{DD}$  voltage drops below  $V_{IT}$  or the nMR pin is driven low, the open-drain nRESET output is asserted. After the  $V_{DD}$  voltage and nMR voltage return above their respective thresholds, the nRESET output remains low within the user-adjustable delay time.

#### **Feature Description**

The SGM829 device has a reset delay time adjustment function and a wide range of detection thresholds, so it can be widely used in a various applications. The detection threshold voltages are factory-set from 1.8V to 5V. In addition, connecting a capacitor between SRT pin and ground allows a programmable reset timeout period from 1.25ms to 10s.

#### Selecting the Reset Delay Time

When the  $V_{DD}$  voltage exceeds the  $V_{DD}$  threshold voltage, a current source will start to charge the SRT capacitor and the SRT voltage will rise. When the SRT voltage exceeds 1.205V, the nRESET voltage will change from low to high.

Therefore, there is a delay time between the point of  $V_{DD}$  reaching its threshold voltage and the nRESET active-high point. The delay time can be calculated according to the following equation:

$T_D(\mu s) = (2.8 \times 10^6) \times C_{SRT}(\mu F) + 290\mu s$  (1)

#### Manual Reset (nMR) Input

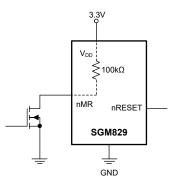

The nMR input allows a processor or other logic circuits to initiate a reset. When nMR is set to logic low  $(0.3V_{DD})$ , the nRESET is asserted. After nMR returns to logic high and  $V_{DD}$  exceeds its reset threshold, nRESET is deasserted after the user-defined reset delay expires. Note that nMR is internally connected to  $V_{DD}$  through a 100k $\Omega$  resistor, so if nMR is not used, this pin can be left open.

Figure 4 shows how to use nMR to monitor multiple system voltages. Note that if the logic signal does not drive nMR fully to  $V_{DD}$ , there will be some extra current drawn into  $V_{DD}$  due to an internal pull-up resistor on nMR. To minimize current draw, an external FET can be used as shown in Figure 5.

Figure 5. Using an External MOSFET to Minimize  $I_{\text{DD}}$  When nMR Signal Does not Go to  $V_{\text{DD}}$

SG Micro Corp

## **DETAILED DESCRIPTION (continued)**

### **nRESET** Output

As long as  $V_{DD}$  voltage exceeds  $V_{IT}$  and the nMR is logic high, nRESET remains high (deasserted). If either  $V_{DD}$  is lower than  $V_{IT}$  or nMR is driven low, nRESET is asserted, driving the nRESET pin to a low-impedance state.

Once the nMR is logic high again and  $V_{DD}$  voltage exceeds  $V_{IT} + V_{HYS}$ , a delay circuit is enabled, keeping nRESET low for a specified reset delay period. Once the reset delay has expired, the nRESET pin enters a high-impedance state. The pull-up resistor from the nRESET pin to the power supply can be used to reset the microprocessor signal to have a voltage above  $V_{DD}$  voltage. The pull-up resistor should be no smaller than 10k $\Omega$  due to the limited nRESET pull-down ability.

#### Device Functional Modes Table 1. Truth Table

| nMR | $V_{DD} > V_{IT}$ | nRESET |

|-----|-------------------|--------|

| L   | 0                 | L      |

| L   | 1                 | L      |

| Н   | 0                 | L      |

| Н   | 1                 | Н      |

#### Normal Operation ( $V_{DD} > V_{DD_{MIN}}$ )

When the V<sub>DD</sub> voltage is higher than V<sub>DD\_MIN</sub>, the logic state of nRESET is determined by V<sub>DD</sub> and the logic state of nMR.

• nMR high: When V<sub>DD</sub> voltage is higher than 1.65V for a selected time ( $t_D$ ), the nRESET logic state corresponds to V<sub>DD</sub> relative to V<sub>IT</sub>.

- nMR low: In this mode, nRESET is held low regardless of  $V_{\text{DD}}$  voltage.

#### Above Power-On Reset but Lower than $V_{DD_MIN}$ ( $V_{POR} < V_{DD} < V_{DD_MIN}$ )

When the V<sub>DD</sub> voltage is lower than V<sub>DD\_MIN</sub> and higher than the power-on reset voltage (V<sub>POR</sub>), the nRESET is asserted and driven to a low-impedance state.

Below Power-On Reset ( $V_{DD} < V_{POR}$ ) When the  $V_{DD}$  voltage is lower than the required voltage ( $V_{POR}$ ), the nRESET voltage is undefined. In the case of nRESET pulling up to  $V_{DD}$  through a 100kΩ resistor, nRESET voltage is equal to or lower than  $V_{DD}$  voltage.

### SGM829

## **APPLICATION INFORMATION**

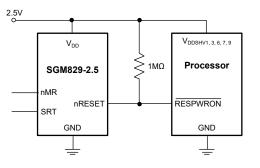

Figure 6 shows a typical application of the SGM829-2.5 used with a 2.5V processor. The nRESET output is typically connected to the nRESET input of a microprocessor. A pull-up resistor is necessary to keep the nRESET logic high when nRESET is not asserted.

Figure 6. Typical Application of the SGM829 with a Processor

#### **Design Requirements**

The SGM829 is intended to drive the nRESET input of a microprocessor. The nRESET pin is pulled high with a 1M $\Omega$  resistor and the reset timeout period is programmed by SRT pin. Leaving SRT open will offer a typical reset timeout period of 0.29ms.

#### **Detailed Design Procedure**

The primary constraint for this application is the reset timeout period. In this case, because SRT is open, the reset timeout period is set to 0.29ms. A  $0.1\mu$ F decoupling capacitor is connected to the V<sub>DD</sub> pin and a 1M $\Omega$  resistor is used to pull the nRESET pin high.

#### **Power Supply Recommendations**

The device is designed to operate from an input supply with a voltage range from 1.65V to 6.5V.

#### **Layout Guidelines**

It is recommended to place a  $0.1\mu$ F ceramic capacitor near the V<sub>DD</sub> pin. If there is no capacitor connected to the SRT pin, parasitic capacitance on this pin should be minimized so the nRESET delay time is not significantly affected.

## **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Changes from Original (MAY 2021) to REV.A

Changed from product preview to production data......All

Page

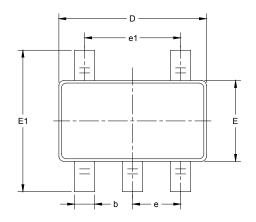

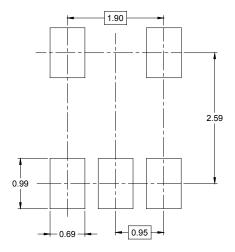

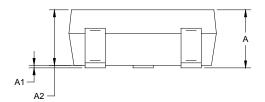

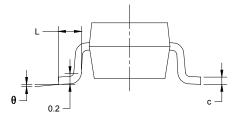

## PACKAGE OUTLINE DIMENSIONS

## SOT-23-5

#### RECOMMENDED LAND PATTERN (Unit: mm)

| Symbol | -         | nsions<br>meters | Dimensions<br>In Inches |       |  |

|--------|-----------|------------------|-------------------------|-------|--|

|        | MIN       | MAX              | MIN                     | MAX   |  |

| A      | 1.050     | 1.250            | 0.041                   | 0.049 |  |

| A1     | 0.000     | 0.100            | 0.000                   | 0.004 |  |

| A2     | 1.050     | 1.150            | 0.041                   | 0.045 |  |

| b      | 0.300     | 0.500            | 0.012                   | 0.020 |  |

| С      | 0.100     | 0.200            | 0.004                   | 0.008 |  |

| D      | 2.820     | 3.020            | 0.111                   | 0.119 |  |

| E      | 1.500     | 1.700            | 0.059                   | 0.067 |  |

| E1     | 2.650     | 2.950            | 0.104                   | 0.116 |  |

| е      | 0.950     | BSC              | 0.037                   | BSC   |  |

| e1     | 1.900 BSC |                  | 0.075                   | BSC   |  |

| L      | 0.300     | 0.600            | 0.012                   | 0.024 |  |

| θ      | 0° 8°     |                  | 0°                      | 8°    |  |

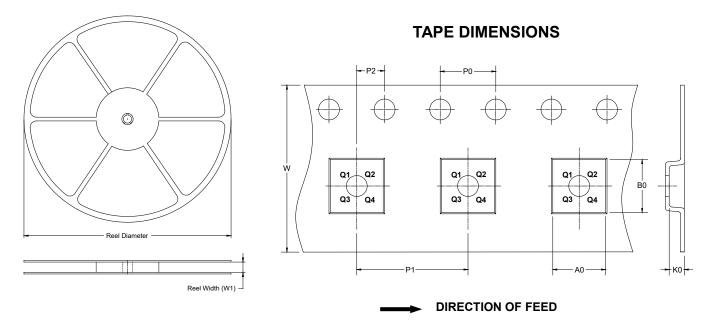

## TAPE AND REEL INFORMATION

### **REEL DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

### KEY PARAMETER LIST OF TAPE AND REEL

| Package Type | Reel<br>Diameter | Reel Width<br>W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|------------------|--------------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| SOT-23-5     | 7″               | 9.5                      | 3.20       | 3.20       | 1.40       | 4.0        | 4.0        | 2.0        | 8.0       | Q3               |

### **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

### **KEY PARAMETER LIST OF CARTON BOX**

| Reel Type   | Length<br>(mm) | Width<br>(mm) | Height<br>(mm) | Pizza/Carton |       |

|-------------|----------------|---------------|----------------|--------------|-------|

| 7" (Option) | 368            | 227           | 224            | 8            |       |

| 7"          | 442            | 410           | 224            | 18           | 00002 |